# Layout Guidelines to Reduce Switch-Node Jitter in the CS51411/NCV51411

Prepared by: Jim Hill ON Semiconductor

ON Semiconductor®

http://onsemi.com

### APPLICATION NOTE

#### Introduction

The CS5141x product family has shown some sensitivity to noise which shows up as jitter on the Switch Node pin (VSW). The CS51411 family uses V<sup>2</sup> control to achieve superior line and load. This control method enhances the load transient response, but under certain conditions can lead to jitter if proper care is not taken. V<sup>2</sup> performs similarly to current mode control, but that the gain is much higher. The gain is set up by the output ripple voltage plus the internal ramp. As you decrease the output voltage, you also decrease

SAMDIC TAY HALL (DESNA)

FOR Many 13/A

FOR MANY 13

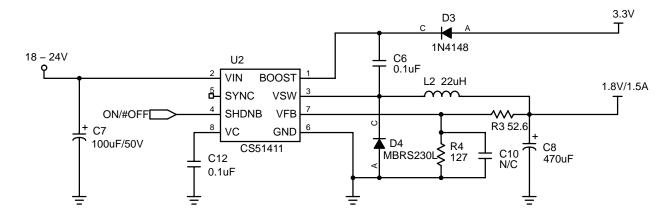

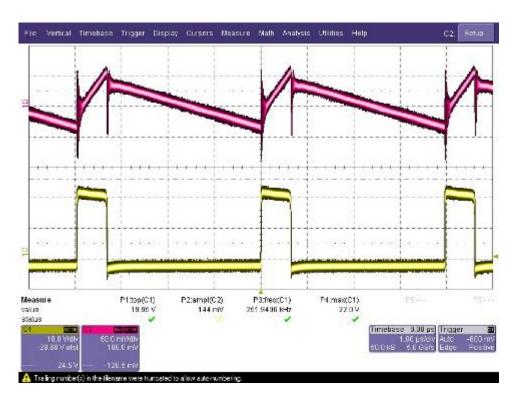

Figure 1. 18 VAC (24 VDC) to 1.8 V/1.4 A

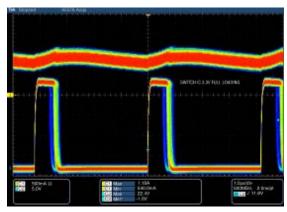

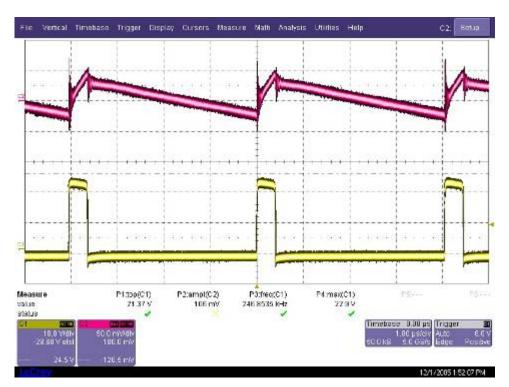

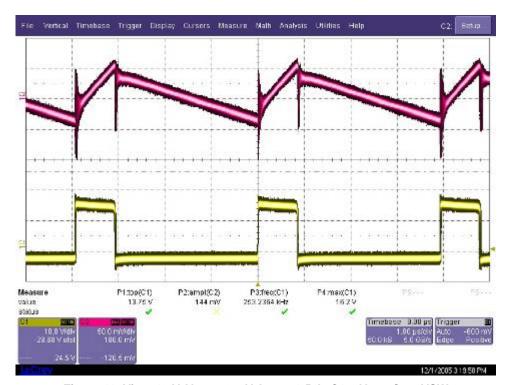

Notice that the jitter at the lower output voltage of  $1.8\ V$  is much worse than that at  $3.3\ V$  which supports the claim in the introduction. The customer was using the

ripple voltage which, in turn, increases gain. With a high gain, the PCB layout becomes very critical. This report shows how minor changes in layout can greatly improve VSW jitter on the CS51411 family of buck converters.

### **Problem**

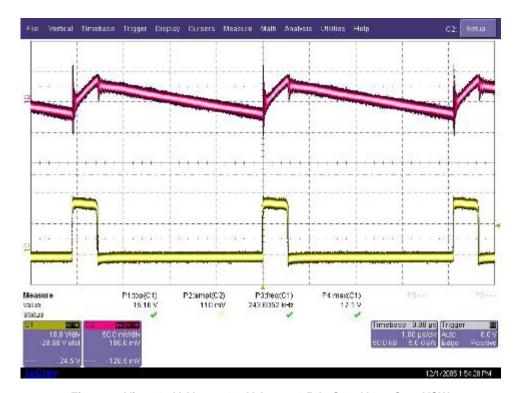

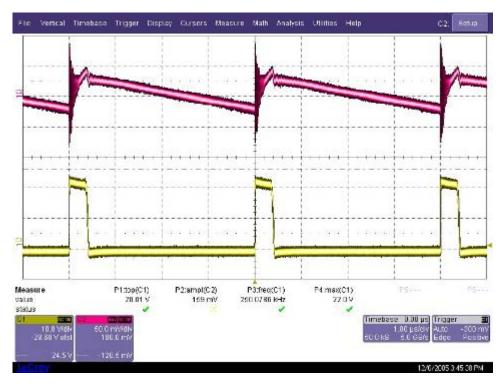

Figures 1 and 2 show examples of this jitter phenomenon. The upper waveform (CH1) is the output voltage and the lower waveform (CH2) is the voltage at VSW.

Figure 2. 18 VAC (24 VDC) to 3.3 V/1.3 A

ON Semiconductor evaluation board with their own components when they noted this behavior.

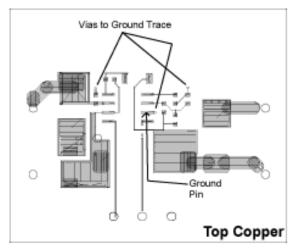

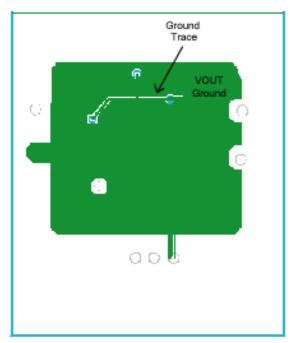

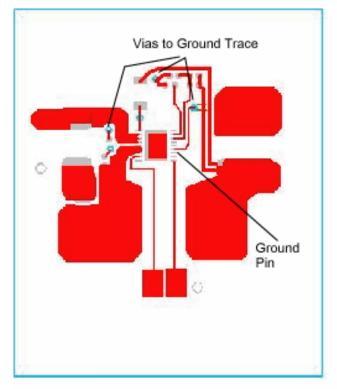

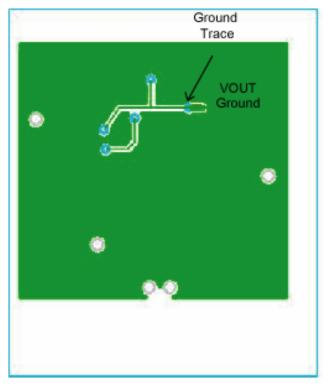

Figure 3. CS51411 Top Metal

One can see that the grounding layout is a high impedance connection that could pick up noise. Also one can see that the actual connection of the ground trace to the ground plane is at the  $V_{\rm IN}$  ground point. Since the input of the buck converter has discontinuous current, this connection could be injecting unwanted noise. Connecting to the output ground should be a better layout due to the continuous current at the output. Connecting directly to the ground plane could also be a better layout.

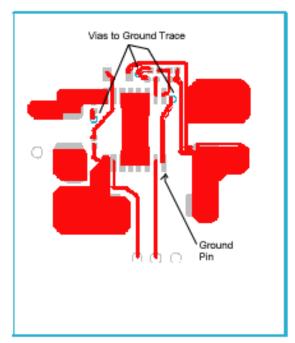

Figure 5. NCV51411 SOIC-16W Top Metal

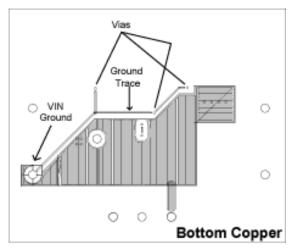

Figure 4. CS51411 Bottom Metal

### **SOIC-16W Layout Evaluation**

As an experiment in layout optimization the NCV51411 evaluation board was utilized. NCV51411 is the same IC in a different package which uses a layout that connects the ground pin to the output ground and the bottom metal ground plane. Figures 5 and 6 show the layout for this board.

Figure 6. NCV51411 SOIC-16W Bottom Metal

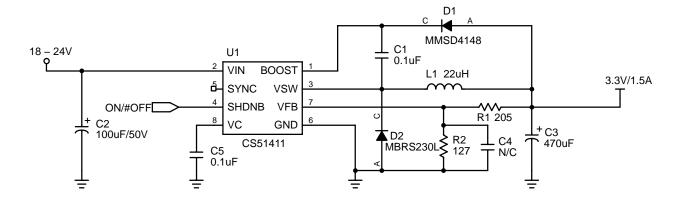

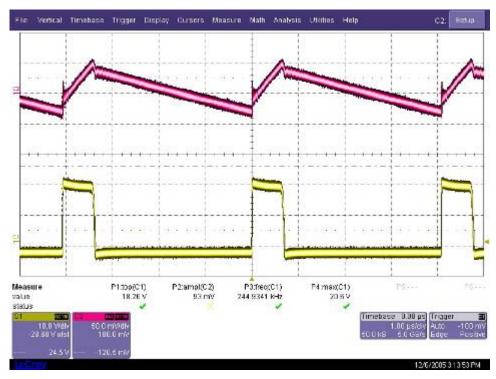

The following waveforms and corresponding schematics show the jitter behavior with this new layout. The input and output capacitor and the inductor are the same as the customer used. The plots are taken with Analog Persistence enabled to plot any changes in the waveform. Figure 7 shows the schematic for the 1.8 V converter which exhibited the

worst jitter behavior when using the original layout. Changing the layout and the decoupling capacitor C10 to 3.3 nF eliminated the jitter problem for this converter. The decoupling capacitor was required to provide a low impedance path to ground for unwanted noise. Figures 8 and 9 show the behavior for the 1.8 V converter.

Figure 7. Schematic for a 1.8 V output converter using the NCV51411 SOIC-16W

Figure 8. Vin = 18 V, Vout = 1.8 V, lout = 1.5 A, C1 = Vout, C2 = VSW

Figure 9. Vin = 24 V, Vout = 1.8 V, lout = 1.5 A, C1 = Vout, C2 = VSW

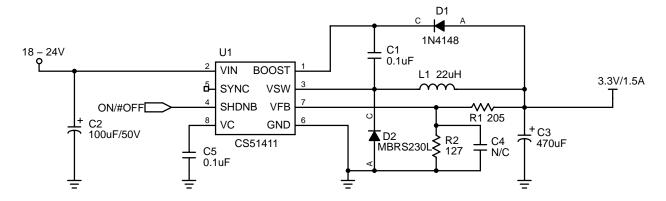

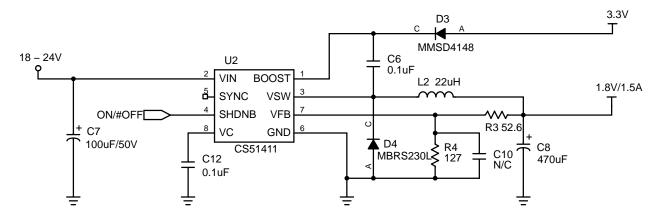

Figure 10 shows the schematic for the 3.3 V converter. This converter did not show as much of jitter due to the higher duty cycle/output voltage. Changing the layout was

all that was necessary to eliminate the jitter problem for this converter. Figures 11 and 12 show the behavior for the  $3.3\ V$  converter.

Figure 10. Schematic for a 3.3 V output converter using the NCV51411 SOIC-16W

Figure 11. Vin = 18 V, Vout = 3.3 V, lout = 1.5 A, C1 = Vout, C2 = VSW

Figure 12. Vin = 24 V, Vout = 3.3 V, lout = 1.5 A, C1 = Vout, C2 = VSW

### **DFN-18 Layout Evaluation**

The same experiment was run on the DFN-18 version of the NCV51411. Figures 13 and 14 show the layout for this

package. Again, the ground connection was made as close as possible to the  $V_{OUT}$  ground connection and the ground plane to reduce noise pickup.

Figure 13. NCV51411 DFN Top Metal

Figure 14. NCV51411 DFN Bottom Metal

Figure 15. Schematic for a 1.8 V output converter using the NCV51411 DFN-18

Figure 16. Vin = 18 V, Vout = 1.8 V, lout = 1.5 A, C1 = Vout, C2 = VSW

Figure 17. Vin = 24 V, Vout = 1.8 V, lout = 1.5 A, C1 = Vout, C2 = VSW

Figure 18. Schematic for a 3.3 V output converter using the NCV51411 DFN-18

Figure 19. Vin = 18 V, Vout = 3.3 V, lout = 1.5 A, C1 = Vout, C2 = VSW

Figure 20. Vin = 24 V, Vout = 3.3 V, lout = 1.5 A, C1 = Vout, C2 = VSW

### **Summary**

The above data shows that with proper layout and decoupling, the jitter in the CS51411 family can be eliminated. Proper layout involves connecting the IC ground close the V<sub>out</sub> ground point, rather than V<sub>in</sub>, and providing a via to a low impedance ground plane to prevent noise

pickup. Also, as pointed out earlier, when you decrease the output voltage, you also decrease ripple voltage which, in turn, increases gain. For lower output voltages noise immunity improves even further by decoupling the feedback pin  $(V_{FB})$ , but the key to eliminating jitter is the layout.

ON Semiconductor and the registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative